**tenx** reserves the right to change or discontinue the manual and online documentation to this product herein to improve reliability, function or design without further notice. **tenx** does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. **tenx** products are not designed, intended, or authorized for use in life support appliances, devices, or systems. If Buyer purchases or uses tenx products for any such unintended or unauthorized application, Buyer shall indemnify and hold tenx and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, cost, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use even if such claim alleges that tenx was negligent regarding the design or manufacture of the part.

# **AMENDMENT HISTORY**

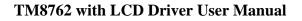

| Version | Date      | Description  |

|---------|-----------|--------------|

| 1.0     | Dec, 2016 | New release. |

# CONTENTS

| AN | AEN                                                                                       | DMENT HISTORY                                                                                                                                                                                                                                                                                                       | .2                                                                               |

|----|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 1. | Ger                                                                                       | eral Description                                                                                                                                                                                                                                                                                                    | .5                                                                               |

|    | 1.1                                                                                       | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                 | .5                                                                               |

|    | 1.2                                                                                       | FEATURES                                                                                                                                                                                                                                                                                                            | .5                                                                               |

|    | 1.3                                                                                       | BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                       | .7                                                                               |

|    | 1.4                                                                                       | PAD DIAGRAM                                                                                                                                                                                                                                                                                                         | .8                                                                               |

|    | 1.5                                                                                       | PAD LIST                                                                                                                                                                                                                                                                                                            | .9                                                                               |

|    | 1.6                                                                                       | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                     | 10                                                                               |

|    | 1.7                                                                                       | CHARACTERISTICS                                                                                                                                                                                                                                                                                                     | 11                                                                               |

|    |                                                                                           | ABSOLOUTE MAXIMUM RATINGS                                                                                                                                                                                                                                                                                           | 11<br>12<br>12<br>12<br>13<br>13                                                 |

|    | 1 8                                                                                       | TYPICAL APPLICATION CIRCUIT                                                                                                                                                                                                                                                                                         | 15                                                                               |

|    | 1.0                                                                                       | I I FICAL APPLICATION CIRCUIT                                                                                                                                                                                                                                                                                       | 13                                                                               |

| 2. |                                                                                           | 8762 Internal System Architecture                                                                                                                                                                                                                                                                                   |                                                                                  |

| 2. | ТМ                                                                                        |                                                                                                                                                                                                                                                                                                                     | 16                                                                               |

| 2. | ТМ                                                                                        | 8762 Internal System Architecture<br>Power Supply                                                                                                                                                                                                                                                                   | 16<br>16                                                                         |

| 2. | TM<br>2.1<br>2.2                                                                          | 8762 Internal System Architecture<br>Power Supply                                                                                                                                                                                                                                                                   | 16<br>16<br>23                                                                   |

| 2. | TM<br>2.1<br>2.2<br>2.3                                                                   | 8762 Internal System Architecture<br>Power Supply<br>SYSTEM CLOCK                                                                                                                                                                                                                                                   | 16<br>16<br>23<br>30                                                             |

| 2. | TM<br>2.1<br>2.2<br>2.3<br>2.4                                                            | 8762 Internal System Architecture<br>Power Supply<br>SYSTEM CLOCK<br>PROGRAM COUNTER (PC)                                                                                                                                                                                                                           | 16<br>16<br>23<br>30<br>32                                                       |

| 2. | TM<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5                                                     | 8762 Internal System Architecture<br>Power Supply<br>SYSTEM CLOCK<br>PROGRAM COUNTER (PC)<br>PROGRAM/TABLE MEMORY                                                                                                                                                                                                   | 16<br>16<br>23<br>30<br>32<br>33                                                 |

| 2. | TM<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6                                              | 8762 Internal System Architecture<br>Power Supply<br>SYSTEM CLOCK                                                                                                                                                                                                                                                   | 16<br>16<br>23<br>30<br>32<br>33<br>33                                           |

| 2. | TM<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6                                              | 8762 Internal System Architecture<br>Power Supply<br>SYSTEM CLOCK                                                                                                                                                                                                                                                   | 16<br>16<br>23<br>30<br>32<br>33<br>34<br>35                                     |

| 2. | TM<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8                                | 8762 Internal System Architecture<br>Power Supply<br>SYSTEM CLOCK                                                                                                                                                                                                                                                   | 16<br>16<br>23<br>30<br>32<br>33<br>34<br>35<br>36                               |

| 2. | TM<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9                         | 8762 Internal System Architecture<br>Power Supply<br>SYSTEM CLOCK                                                                                                                                                                                                                                                   | 16<br>16<br>23<br>30<br>32<br>33<br>34<br>35<br>36<br>36                         |

| 2. | TM<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10                 | 8762 Internal System Architecture<br>Power Supply<br>SYSTEM CLOCK<br>PROGRAM COUNTER (PC)<br>PROGRAM/TABLE MEMORY<br>INDEX ADDRESS REGISTER (@HL)<br>STACK REGISTER (STACK)<br>DATA MEMORY (RAM)<br>WORKING REGISTER (WR)<br>ACCUMULATOR (AC)<br>ALU (Arithmetic and Logic Unit)                                    | 16<br>16<br>23<br>30<br>32<br>33<br>34<br>35<br>36<br>36<br>36                   |

| 2. | TM<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11         | 8762 Internal System Architecture<br>Power Supply<br>SYSTEM CLOCK<br>PROGRAM COUNTER (PC)<br>PROGRAM/TABLE MEMORY<br>INDEX ADDRESS REGISTER (@HL)<br>STACK REGISTER (STACK)<br>DATA MEMORY (RAM)<br>WORKING REGISTER (WR)<br>ACCUMULATOR (AC)<br>ALU (Arithmetic and Logic Unit)<br>BINARY CONVERT TO DECIMAL (BCD) | 16<br>16<br>23<br>30<br>32<br>33<br>34<br>35<br>36<br>36<br>36<br>36             |

| 2. | TM<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11<br>2.12 | 8762 Internal System Architecture<br>Power Supply<br>SYSTEM CLOCK<br>PROGRAM COUNTER (PC)<br>PROGRAM/TABLE MEMORY<br>INDEX ADDRESS REGISTER (@HL)<br>STACK REGISTER (STACK)<br>DATA MEMORY (RAM)<br>WORKING REGISTER (WR)<br>ACCUMULATOR (AC)<br>ALU (Arithmetic and Logic Unit)                                    | 16<br>16<br>23<br>30<br>32<br>33<br>34<br>35<br>36<br>36<br>36<br>36<br>36<br>38 |

\_\_\_\_\_

|    | 2.15                                                                                                                             | CONTROL REGISTER (CTL)                                                                                                                                                                                                                                                                                                                     | 0                                              |

|----|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

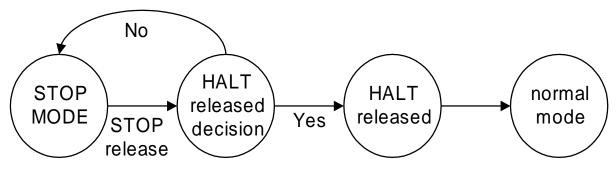

|    | 2.16                                                                                                                             | HALT FUNCTION                                                                                                                                                                                                                                                                                                                              | 3                                              |

|    | 2.17                                                                                                                             | STOP FUNCTION (STOP)                                                                                                                                                                                                                                                                                                                       | 4                                              |

|    | 2.18                                                                                                                             | BACK UP FUNCTION                                                                                                                                                                                                                                                                                                                           | 5                                              |

| 3. | Con                                                                                                                              | trol Function                                                                                                                                                                                                                                                                                                                              | 7                                              |

|    | 3.1                                                                                                                              | NTERRUPT FUNCTION                                                                                                                                                                                                                                                                                                                          | 7                                              |

|    | 3.2                                                                                                                              | RESET FUNCTION                                                                                                                                                                                                                                                                                                                             | 1                                              |

|    | 3.3                                                                                                                              | CLOCK GENERATOR                                                                                                                                                                                                                                                                                                                            | 5                                              |

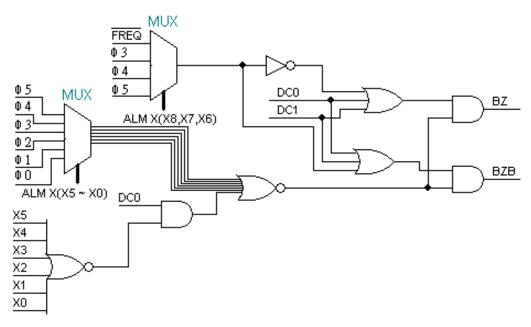

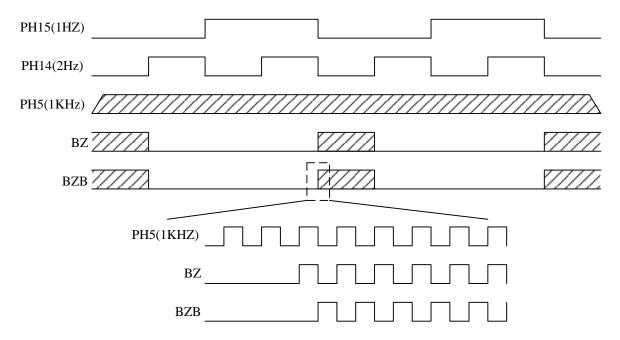

|    | 3.4                                                                                                                              | BUZZER OUTPUT PINS                                                                                                                                                                                                                                                                                                                         | 8                                              |

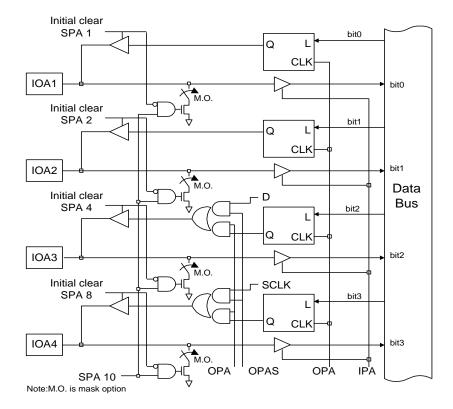

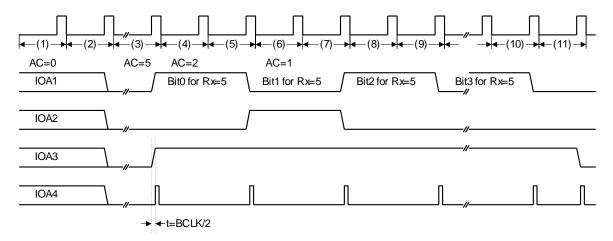

|    | 3.5                                                                                                                              | INPUT/OUTPUT PORTS                                                                                                                                                                                                                                                                                                                         | 0                                              |

|    | 3.6                                                                                                                              | EL PANEL DRIVER                                                                                                                                                                                                                                                                                                                            | 7                                              |

|    | 3.7                                                                                                                              | EXTERNAL INT PIN                                                                                                                                                                                                                                                                                                                           | 9                                              |

|    | 3.8                                                                                                                              | Resistor to Frequency Converter (RFC)                                                                                                                                                                                                                                                                                                      | 0                                              |

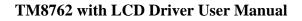

|    | 3.9                                                                                                                              | Key-Matrix Scanning Function                                                                                                                                                                                                                                                                                                               | 5                                              |

| 4  | ICI                                                                                                                              |                                                                                                                                                                                                                                                                                                                                            | 0                                              |

| 4. | LU                                                                                                                               | D/LED DRIVER OUTPUT                                                                                                                                                                                                                                                                                                                        | ,                                              |

| 4. |                                                                                                                                  | LCD DRIVER OUTPUT                                                                                                                                                                                                                                                                                                                          |                                                |

| 4. | 4.1                                                                                                                              |                                                                                                                                                                                                                                                                                                                                            | 9                                              |

|    | 4.1<br>4.2                                                                                                                       | LCD DRIVER OUTPUT                                                                                                                                                                                                                                                                                                                          | 9<br>7                                         |

|    | 4.1<br>4.2<br>Deta                                                                                                               | LCD DRIVER OUTPUT                                                                                                                                                                                                                                                                                                                          | 9<br>7<br>0                                    |

|    | 4.1<br>4.2<br>Deta<br>5.1                                                                                                        | LCD DRIVER OUTPUT                                                                                                                                                                                                                                                                                                                          | 9<br>7<br>0                                    |

|    | 4.1<br>4.2<br>Deta<br>5.1<br>5.2                                                                                                 | LCD DRIVER OUTPUT                                                                                                                                                                                                                                                                                                                          | 9<br>7<br>0<br>0                               |

|    | <ul> <li>4.1</li> <li>4.2</li> <li>Deta</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> </ul>                                        | LCD DRIVER OUTPUT                                                                                                                                                                                                                                                                                                                          | 9<br>7<br>0<br>5<br>6                          |

|    | <ul> <li>4.1</li> <li>4.2</li> <li>Deta</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ul>                           | LCD DRIVER OUTPUT89LED DRIVER OUTPUT97ail Explanation of TM8762 Instructions110INPUT / OUTPUT INSTRUCTIONS110ACCUMULATOR MANIPULATION INSTRUCTIONS AND MEMORY115MANIPULATION INSTRUCTIONS115OPERATION INSTRUCTIONS110                                                                                                                      | 9<br>7<br>0<br>5<br>5<br>6<br>3                |

|    | <ul> <li>4.1</li> <li>4.2</li> <li>Deta</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> </ul>                           | LCD DRIVER OUTPUT89LED DRIVER OUTPUT97ail Explanation of TM8762 Instructions110INPUT / OUTPUT INSTRUCTIONS110ACCUMULATOR MANIPULATION INSTRUCTIONS AND MEMORY115MANIPULATION INSTRUCTIONS115OPERATION INSTRUCTIONS116LOAD/STORE INSTRUCTIONS125                                                                                            | 9<br>7<br>0<br>5<br>6<br>3<br>4                |

|    | <ul> <li>4.1</li> <li>4.2</li> <li>Deta</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul>              | LCD DRIVER OUTPUT89LED DRIVER OUTPUT97ail Explanation of TM8762 Instructions110INPUT / OUTPUT INSTRUCTIONS110ACCUMULATOR MANIPULATION INSTRUCTIONS AND MEMORY114MANIPULATION INSTRUCTIONS114OPERATION INSTRUCTIONS116LOAD/STORE INSTRUCTIONS124CPU CONTROL INSTRUCTIONS124                                                                 | 9<br>7<br>0<br>5<br>6<br>3<br>4<br>7           |

|    | <ul> <li>4.1</li> <li>4.2</li> <li>Deta</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> </ul> | LCD DRIVER OUTPUT89LED DRIVER OUTPUT97ail Explanation of TM8762 Instructions110INPUT / OUTPUT INSTRUCTIONS110ACCUMULATOR MANIPULATION INSTRUCTIONS AND MEMORY114MANIPULATION INSTRUCTIONS114OPERATION INSTRUCTIONS116LOAD/STORE INSTRUCTIONS122CPU CONTROL INSTRUCTIONS124INDEX ADDRESS INSTRUCTIONS127                                    | 9<br>7<br>0<br>5<br>6<br>3<br>4<br>7           |

|    | 4.1<br>4.2<br>Det:<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8                                                       | LCD DRIVER OUTPUT89LED DRIVER OUTPUT.97ail Explanation of TM8762 Instructions110INPUT / OUTPUT INSTRUCTIONS110ACCUMULATOR MANIPULATION INSTRUCTIONS AND MEMORY111MANIPULATION INSTRUCTIONS111OPERATION INSTRUCTIONS110LOAD/STORE INSTRUCTIONS122CPU CONTROL INSTRUCTIONS124INDEX ADDRESS INSTRUCTIONS127DECIMAL ARITHMETIC INSTRUCTIONS127 | 9<br>7<br>0<br>5<br>6<br>3<br>4<br>7<br>8      |

| 5. | 4.1<br>4.2<br>Det:<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9                                                | LCD DRIVER OUTPUT89LED DRIVER OUTPUT92ail Explanation of TM8762 Instructions110INPUT / OUTPUT INSTRUCTIONS110ACCUMULATOR MANIPULATION INSTRUCTIONS AND MEMORY111MANIPULATION INSTRUCTIONS112OPERATION INSTRUCTIONS112CPU CONTROL INSTRUCTIONS124INDEX ADDRESS INSTRUCTIONS122JUMP INSTRUCTIONS124JUMP INSTRUCTIONS124                      | 9<br>7<br>0<br>5<br>6<br>3<br>4<br>7<br>8<br>9 |

# 1. General Description

# **1.1 GENERAL DESCRIPTION**

The TM8762 is an embedded high-performance 4-bit micro-controller with LCD/LED driver on a chip. It contains all the necessary functions for a micro-controller, such as 4-bit parallel processing ALU, ROM, RAM, I/O ports, timer, clock generator, dual clock operation, Resistance to Frequency Converter(RFC), EL panel driver, LCD driver, look-up table, watchdog timer and key matrix scanning circuitry etc. on a single chip.

# **1.2 FEATURES**

- **1.** Low power dissipation.

- **2.** Powerful instruction set (143 instructions).

- Binary addition subtraction, BCD conversion, logical operation in direct and index addressing mode.

- Single-bit manipulation (set, reset, decision for branch).

- Various conditional branches.

- 16 working registers and manipulation.

- Look-up Table.

- LCD driver with data transfer.

- **3.** Memory capacity.

- ROM capacity 2048 x 16 bits.

- RAM capacity 128 x 4 bits.

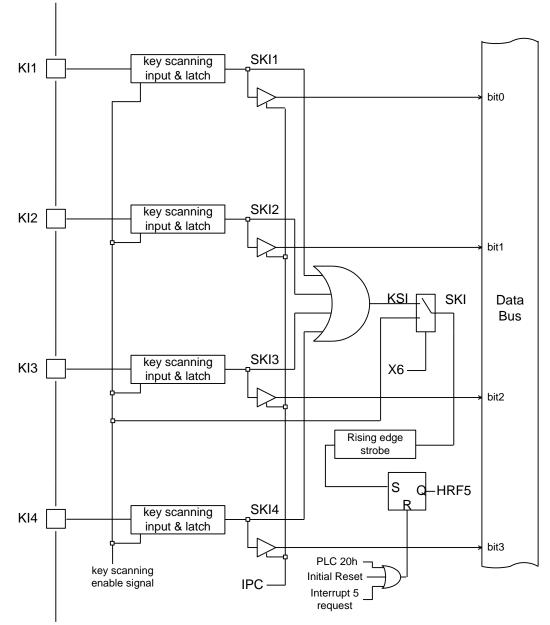

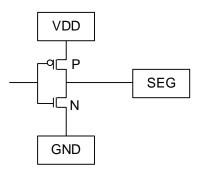

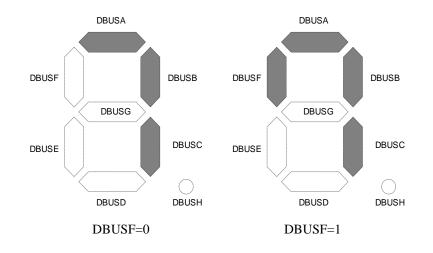

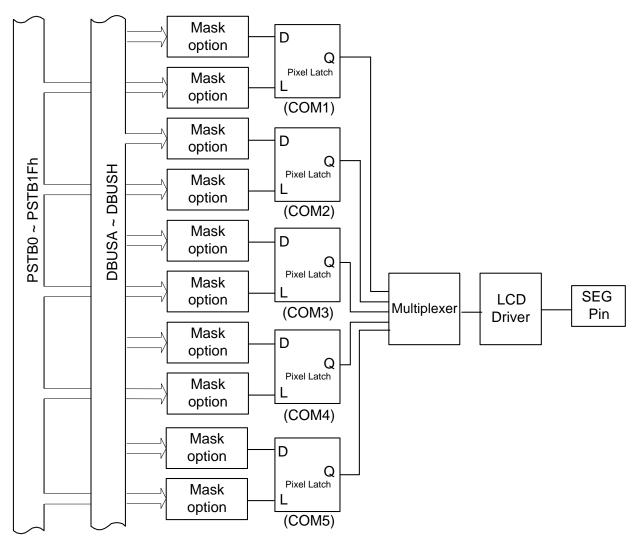

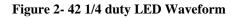

- **4.** LCD/LED driver output.

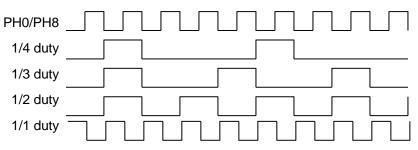

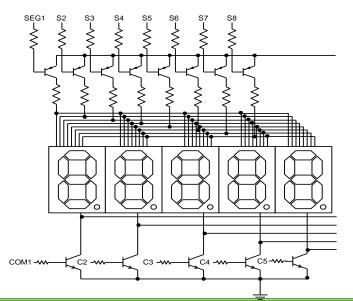

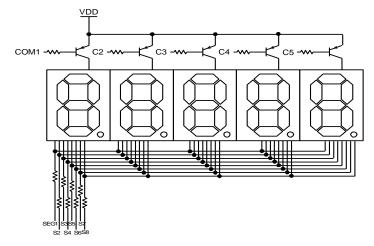

- 5 common outputs and 35 segment outputs (drive up to 175 LCD/LED segments).

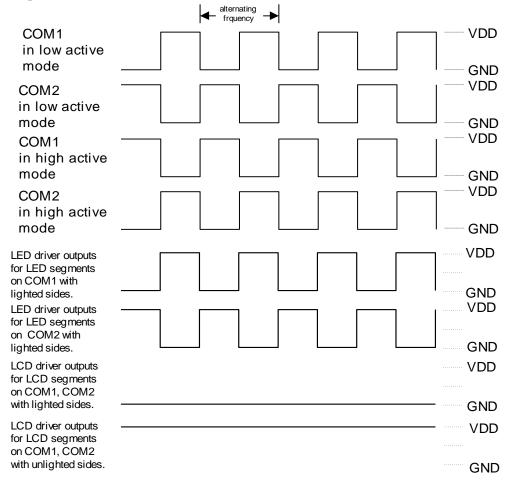

- 1/2 Duty, 1/3 Duty, 1/4 Duty or 1/5 Duty for both LCD/LED drivers selectable in mask option.

- 1/2 Bias or 1/3 Bias for LCD driver selectable in mask option.

- Single instruction to turn off all segments.

- All segment outputs can be defined as CMOS or P\_open drain output type in mask option.

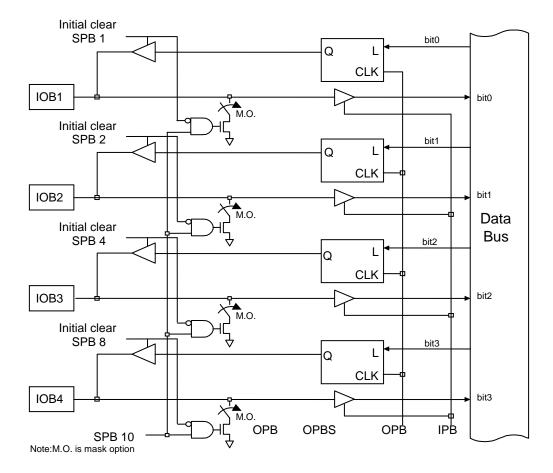

- **5.** Input/output ports.

- Port IOA 4 pins (with internal pull-low), muxed with SEG24~27.

- Port IOB 4 pins (with internal pull-low), muxed with SEG28~31.

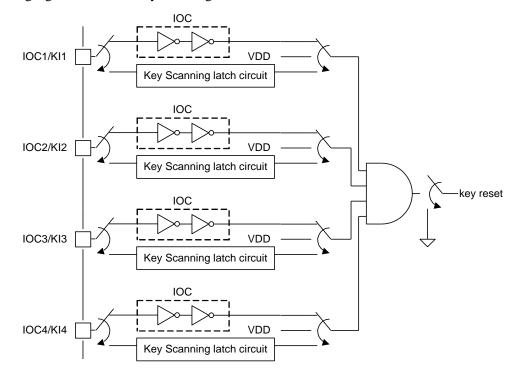

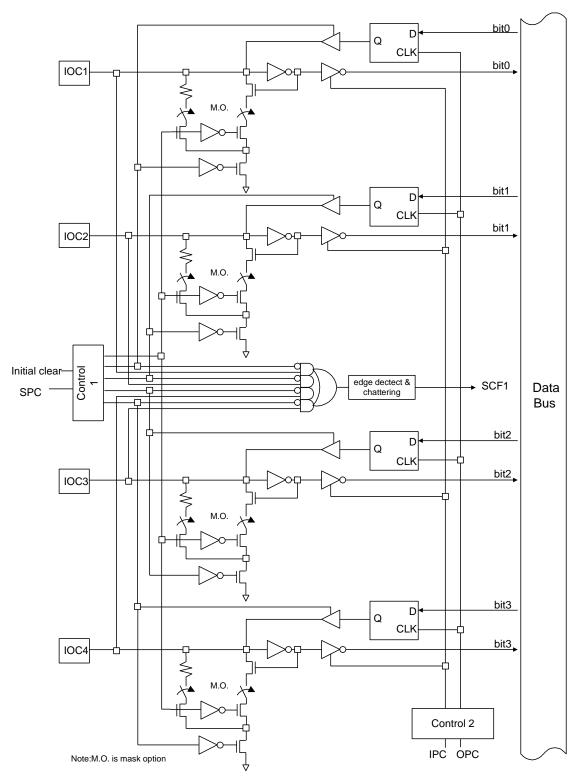

- Port IOC 4 pins (with internal pull-low/ low-level-hold), muxed with SEG32~35. IOC port with built-in input signal chattering prevention circuitry.

- **6.** 8 level subroutine nesting.

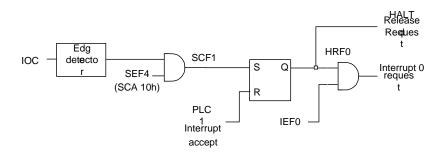

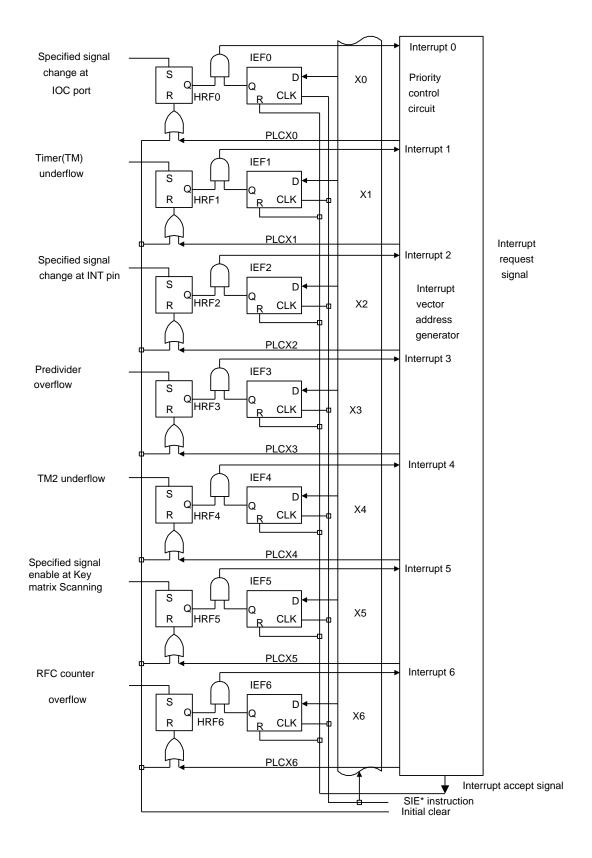

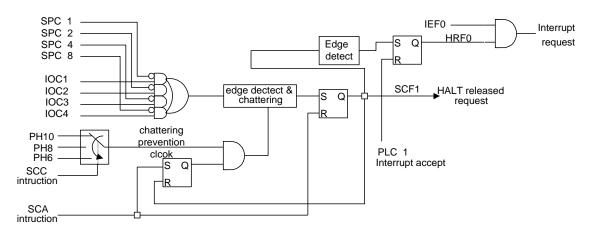

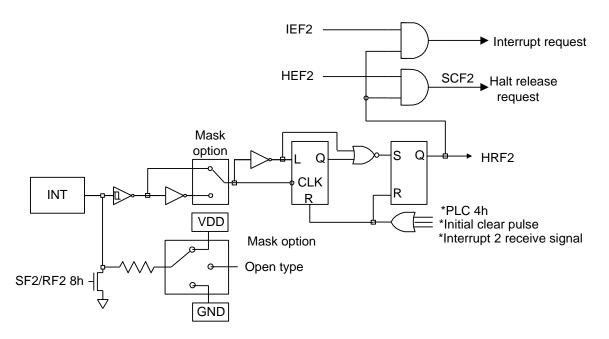

- 7. Interrupt function.

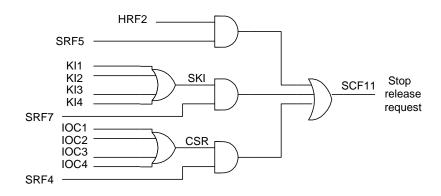

- External factors 3 (INT pin, Port IOC & KI input).

- Internal factors 4 (Pre-Divider, Timer1, Timer2 & RFC).

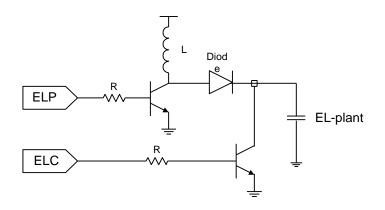

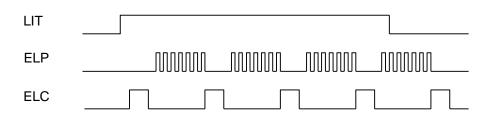

- **8.** Built-in EL panel driver.

- ELC, ELP (Muxed with SEG28, SEG29).

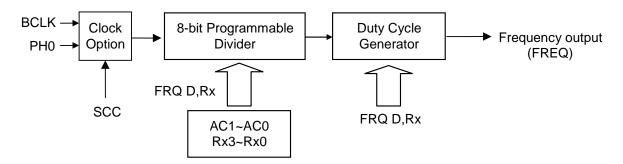

- 9. Built-in Alarm, clock or single tone melody generator.

- BZB, BZ (Muxed with SEG30, SEG31).

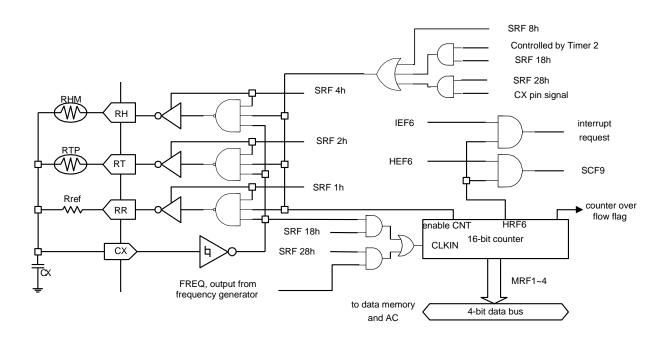

- **10.** Built-in R to F Converter circuit.

- CX, RR, RT, RH (Muxed with SEG24~SEG27).

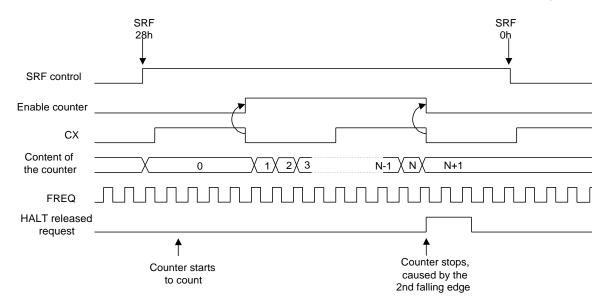

- **11.** Built-in key matrix scanning function.

- K1~K16 (Shared with SEG1~SEG16).

- KI1~KI4 (Muxed with SEG32~SEG35).

- 12. Two 6-bit programmable timers with programmable clock source.

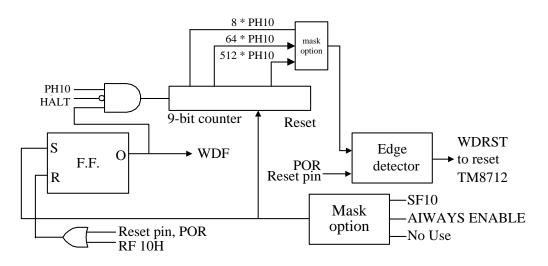

- 13. Watch dog timer.

- 14. Built-in Voltage doubler, halver, tripler charge pump circuit.

- **15.** Dual clock operation

- Slow clock oscillation can be defined as X'tal or external RC type oscillator in mask option.

- Fast clock oscillation can be defined as internal R or external R type oscillator in mask option.

**16.** HALT function.

**17.** STOP function.

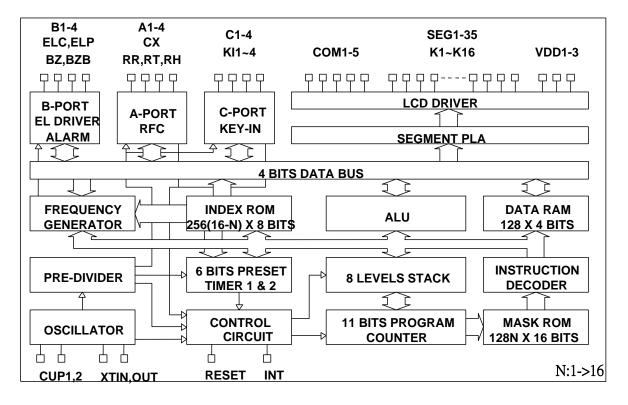

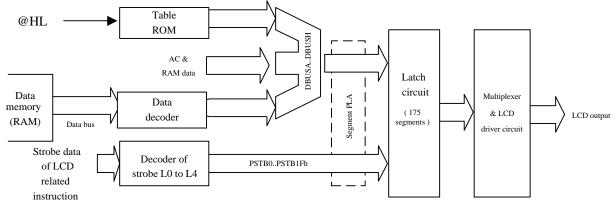

# **1.3 BLOCK DIAGRAM**

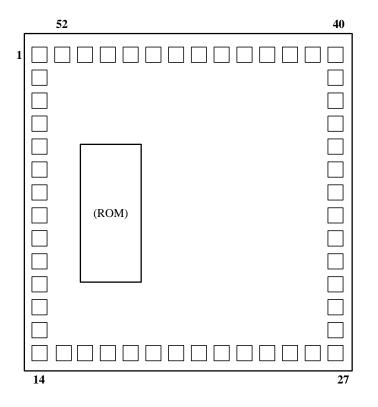

# **1.4 PAD DIAGRAM**

The chip substrate should be connected to GND.

# 1.5 PAD LIST

| No | Name      | No                | Name           |

|----|-----------|-------------------|----------------|

| 1  | BAK       | 27                | SEG13/K13      |

| 2  | XIN       | 28                | SEG14/K14      |

| 3  | XOUT      | 29                | SEG15/K15      |

| 4  | GND       | 30                | SEG16/K16      |

| 5  | VDD1      | 31                | SEG17          |

| 6  | VDD2      | 32                | SEG18          |

| 7  | VDD3      | 33                | SEG19          |

| 8  | CUP1      | 34                | SEG20          |

| 9  | CUP2      | 35                | SEG21          |

| 10 | COM1      | 36                | SEG22          |

| 11 | COM2      | 37                | SEG23          |

| 12 | COM3      | 38                | SEG24/IOA1/CX  |

| 13 | COM4      | 39                | SEG25/IOA2/RR  |

| 14 | COM5      | 40                | SEG26/IOA3/RT  |

| 15 | SEG1/K1   | 41                | SEG27/IOA4/RH  |

| 16 | SEG2/K2   | 42 SEG28/IOB1/ELC |                |

| 17 | SEG3/K3   | 43                | SEG29/IOB2/ELP |

| 18 | SEG4/K4   | 44                | SEG30/IOB3/BZB |

| 19 | SEG5/K5   | 45                | SEG31/IOB4/BZ  |

| 20 | SEG6/K6   | 46                | SEG32/IOC1/KI1 |

| 21 | SEG7/K7   | 47                | SEG33/IOC2/KI2 |

| 22 | SEG8/K8   | 48                | SEG34/IOC3/KI3 |

| 23 | SEG9/K9   | 49                | SEG35/IOC4/KI4 |

| 24 | SEG10/K10 | 50                | RESET          |

| 25 | SEG11/K11 | 51                | INT            |

| 26 | SEG12/K12 | 52                | TEST           |

# **1.6 PIN DESCRIPTION**

| Name           | I/O    | Description                                                                                                                                                                                                                                                                                |

|----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BAK            | Р      | Positive Back-up voltage.<br>In Li power Mode, connect a 0.1u capacitor to GND.                                                                                                                                                                                                            |

| VDD1,2,3       | Р      | <ul><li>LCD supply voltage, and positive supply voltage.</li><li>In Ag Mode, it will connect a positive power to VDD1.</li><li>In Li or ExtV power mode, it will connect a positive power to VDD2.</li></ul>                                                                               |

| RESET          | Ι      | Input pin for external reset request signal. Built-in internal pull-down resistor.                                                                                                                                                                                                         |

| INT            | I      | <ul><li>Input pin for external INT request signal.</li><li>It can be trigger by Falling edge or rising edge and is defined in mask option.</li><li>nternal pull-down or pull-up resistor is defined in mask option.</li></ul>                                                              |

| TESTA          | Ι      | Test signal input pin.                                                                                                                                                                                                                                                                     |

| CUP1,2         | 0      | <ul> <li>Switching pins for supplying the LCD driving voltage to the VDD1, 2, 3 pins.</li> <li>Connect the CUP1 and CUP2 pins with non-polarized electrolytic capacitor when chip operates in 1/2 or 1/3 bias mode.</li> </ul>                                                             |

|                |        | n no BIAS mode application, leave these pins open.                                                                                                                                                                                                                                         |

| XIN<br>XOUT    | I<br>O | <ul> <li>Input /Output pins for slow clock oscillator.</li> <li>32KHz Crystal oscillator.</li> <li>In FAST mode, connect an external resistor to form a RC oscillator (mask option).</li> <li>In SLOW mode, connect an external resistor to form a RC oscillator (mask option).</li> </ul> |

| COM1~5         | 0      | Output pins for driving the common pins for the LCD or LED panel.                                                                                                                                                                                                                          |

| SEG1-35        | 0      | Output pins for driving the LCD or the LED panel segment.                                                                                                                                                                                                                                  |

| IOA1-4         | I/O    | Input / Output port A. (Muxed with SEG24~SEG27)                                                                                                                                                                                                                                            |

| IOB1-4         | I/O    | Input / Output port B. (Muxed with SEG28~SEG31)                                                                                                                                                                                                                                            |

| IOC1-4         | I/O    | Input / Output port C. (Muxed with SEG32~SEG35)                                                                                                                                                                                                                                            |

| CX<br>RR/RT/RH | I<br>O | RFC application with 1 input pin and 3 output pins. (Muxed with SEG24~SEG27)                                                                                                                                                                                                               |

| ELC/ELP        | 0      | Output port for the EL panel driver. (Muxed with SEG28,SEG29)                                                                                                                                                                                                                              |

| BZB/BZ         | 0      | Output port for alarm, clock or the single melody tone generator.<br>(Muxed with SEG30~SEG31)                                                                                                                                                                                              |

| K1~K16         | 0      | Output port for the key matrix scanning.(Shared with SEG1~SEG16)                                                                                                                                                                                                                           |

| KI1~4          | Ι      | Input port for the key matrix scanning.(Muxed with SEG32~SEG35)                                                                                                                                                                                                                            |

| GND            | Р      | Negative supply voltage.                                                                                                                                                                                                                                                                   |

# **1.7 CHARACTERISTICS**

# ABSOLOUTE MAXIMUM RATINGS

GND=0V

| Name                          | Symbol | Range              | Unit |

|-------------------------------|--------|--------------------|------|

|                               | VDD1   | -0.3 to 5.5        |      |

| Maximum Supply Voltage        | VDD2   | -0.3 to 5.5        |      |

| Waxiniun Suppry Voltage       | VDD3   | -0.3 to 8.5        | V    |

| Maximum Input Voltage         | Vin    | -0.3 to VDD1/2+0.3 | v    |

| Maximum autnut Valtaga        | Vout1  | -0.3 to VDD1/2+0.3 |      |

| Maximum output Voltage        | Vout2  | -0.3 to VDD3+0.3   |      |

| Maximum Operating Temperature | Topg   | -20 to +70         | °C   |

| Maximum Storage Temperature   | Tstg   | -25 to +125        | C    |

# **POWER CONSUMPTION**

at Ta=  $-20^{\circ}$ C to  $70^{\circ}$ C, GND=0V

| Name      | Sym.   | Condition                                                                                             | Min. | Typ. | Max. | Unit |

|-----------|--------|-------------------------------------------------------------------------------------------------------|------|------|------|------|

| HALT mode | IHALT1 | Only the 32.768KHz Crystal oscillator is<br>operating without loading.<br>Ag mode, VDD1=1.5V, BCF = 0 |      | 2    | 5    |      |

| HAL1 mode | IHALT2 | Only 32.768KHz Crystal oscillator is<br>operating, without loading.<br>Li mode, VDD2=3.0V, BCF = 0    |      | 2    | 5    | uA   |

| STOP mode | ISTOP  |                                                                                                       |      |      | 1    |      |

Note : When using RC oscillator, the current consumption will depend on the frequency of oscillation.

# ALLOWABLE OPERATING CONDITIONS

at Ta= -20°C to 70°C, GND=0V

| Name                        | Symb. | Condition                   | Min.     | Max.     | Unit |

|-----------------------------|-------|-----------------------------|----------|----------|------|

|                             | VDD1  |                             | 1.2      | 5.25     |      |

| Supply Voltage              | VDD2  |                             | 2.4      | 5.25     |      |

|                             | VDD3  |                             | 2.4      | 8.0      |      |

| Oscillator Start-Up Voltage | VDDB  | Crustal Mode                | 1.3      |          |      |

| Oscillator Sustain Voltage  | VDDB  | Crystal Mode                | 1.2      |          |      |

| Supply Voltage              | VDD1  | Ag Mode                     | 1.2      | 1.65     |      |

| Supply Voltage              | VDD2  | EXT-V, Li Mode              | 2.4      | 5.25     |      |

| Input "H" Voltage           | Vih1  | A a Dattamy Mada            | VDD1-0.7 | VDD1+0.7 |      |

| Input "L" Voltage           | Vil1  | Ag Battery Mode             | -0.7     | 0.7      |      |

| Input "H" Voltage           | Vih2  | Li Dottom: Modo             | VDD2-0.7 | VDD2+0.7 | V    |

| Input "L" Voltage           | Vil2  | Li Battery Mode             | -0.7     | 0.7      |      |

| Input "H" Voltage Vih       |       | OSCIN in A g Pottomy Mode   | 0.8xVDD1 | VDD1     |      |

| Input "L" Voltage           | Vil3  | OSCIN in Ag Battery Mode    | 0        | 0.2xVDD1 |      |

| Input "H" Voltage           | Vih4  |                             | 0.8xVDD2 | VDD2     |      |

| Input "L" Voltage           | Vil4  | OSCIN in Li Battery Mode    | 0        | 0.2xVDD2 |      |

| Input "H" Voltage           | Vih5  | CFIN in Li Battery or EXT-V | 0.8xVDD2 | VDD2     |      |

| Input "L" Voltage           | Vil5  | Mode                        | 0        | 0.2xVDD2 |      |

| Input "H" Voltage           | Vih6  | DC Mada                     | 0.8xVDDO | VDDO     |      |

| Input "L" Voltage           | Vil6  | RC Mode                     | 0        | 0.2xVDDO |      |

| Operating Free              | Fopg1 | Crystal Mode                | 32       |          | KHz  |

| Operating Freq              | Fopg2 | RC Mode                     | 10       | 1000     | КΠΖ  |

# INTERNAL RC FREQUENCY RANGE

| Option Mode | Mode BAK Min |        | Тур.    | Max.    |

|-------------|--------------|--------|---------|---------|

| 250 KHz     | 1.5V         | 200KHz | 300 KHz | 400 KHz |

| 230 KHZ     | 3.0V         | 200KHz | 250 KHz | 300 KHz |

| 500 KHz     | 1.5V         | 450KHz | 600 KHz | 750 KHz |

| 300 KHZ     | 3.0V         | 400KHz | 500 KHz | 600 KHz |

# ALLOWABLE OPERATING FREQUENCY

at Ta=-20°C to 70°C,GND= 0V

| Condition       | Max, Operating Frequency |  |  |

|-----------------|--------------------------|--|--|

| BAK=1.5V (VDD1) | 800KHz                   |  |  |

| BAK=3V (VDD2)   | 4MHz                     |  |  |

# **ELECTRICAL CHARACTERISTICS**

at#1:VDD1=1.2V(Ag);

at#2:VDD2=2.4V(Li):

at#3:VDD2=4V(Ext-V);

### Input Resistance

| Name                   | Symb.  | Condition         | Min.                                                               | Тур. | Max. | Unit |

|------------------------|--------|-------------------|--------------------------------------------------------------------|------|------|------|

|                        | Rllh1  | Vi=0.2VDD1,#1     | 10                                                                 | 40   | 100  |      |

| "L" Level Hold Tr(IOC) | Rllh2  | Vi=0.2VDD2,#2     | 10                                                                 | 40   | 100  |      |

|                        | Rllh3  | Vi=0.2VDD2,#3     | 5                                                                  | 20   | 50   |      |

|                        | Rmad1  | Vi=VDD1,#1        | 200                                                                | 500  | 1000 |      |

| IOA/B/C Pull-Down Tr   | Rmad2  | Vi=VDD2,#2        | 200                                                                | 500  | 1000 |      |

|                        | Rmad3  | Vi=VDD2,#3        | 100                                                                | 250  | 500  |      |

| INT Pull-up Tr         | Rintu1 | Vi=VDD1,#1        | 200                                                                | 500  | 1000 | ΚΩ   |

|                        | Rintu2 | Vi=VDD2,#2        | 200                                                                |      |      |      |

|                        | Rintu3 | Vi=VDD2,#3        | 200         500         1000           100         250         500 |      |      |      |

|                        | Rintd1 | Vi=GND,#1         | 200                                                                | 500  | 1000 |      |

| INT Pull-Down Tr       | Rintd2 | Vi=GND,#2         | 200                                                                | 500  | 1000 |      |

|                        | Rintd3 | Vi=GND,#3         | 100                                                                | 250  | 500  |      |

|                        | Rres1  | Vi=GND or VDD1,#1 |                                                                    |      |      |      |

| RES Pull-Down R        | Rres2  | Vi=GND or VDD2,#2 | 10                                                                 | 40   | 100  |      |

|                        | Rres3  | Vi=GND or VDD2,#3 |                                                                    |      |      |      |

# **DC Output Characteristics**

| Name               | Symb. | Condition     | Port    | Min. | Тур. | Max. | Unit |

|--------------------|-------|---------------|---------|------|------|------|------|

|                    | Voh1c | Ioh=-200uA,#1 |         | 0.8  | 0.9  | 1.0  |      |

| Output "H" Voltage | Voh2c | Ioh=-1mA,#2   | SEG1~35 | 1.5  | 1.8  | 2.1  |      |

|                    | Voh3c | Ioh=-3mA,#3   |         | 2.5  | 3.0  | 3.5  | v    |

|                    | Vol1c | Iol=400uA,#1  | SEG1~55 | 0.2  | 0.3  | 0.4  | v    |

| Output "L" Voltage | Vol2c | Iol=2mA,#2    |         | 0.3  | 0.6  | 0.9  |      |

|                    | Vol3c | Iol=6mA,#3    |         | 0.5  | 1.0  | 1.5  |      |

# **Segment Driver Output Characteristics**

| Name                | Symb.  | Condition           | For   | Min. | Тур. | Max. | Unit |

|---------------------|--------|---------------------|-------|------|------|------|------|

|                     |        | Static Display N    | Mode  |      |      |      |      |

|                     | Voh1d  | Ioh=-1uA,#1         |       | 2.2  |      |      |      |

| Output "H" Voltage  | Voh2d  | Ioh=-1uA,#2         |       | 2.2  |      |      |      |

|                     | Voh3d  | Ioh=-1uA,#3         | SEC - | 3.8  |      |      |      |

|                     | Vol1d  | Iol=1uA,#1          | SEG-n |      |      | 0.2  |      |

| Output "L" Voltage  | Vol2d  | Iol=1uA,#2          |       |      |      | 0.2  |      |

|                     | Vol3d  | Iol=1uA,#3          |       |      |      | 0.2  | V    |

|                     | Voh1e  | Ioh=-10uA,#1        |       | 2.2  |      |      | V    |

| Output "H" Voltage  | Voh2e  | Ioh=-10uA,#2        |       | 2.2  |      |      |      |

|                     | Voh3e  | Ioh=-10uA,#3        | COM   | 3.8  |      |      |      |

|                     | Vol1e  | Iol=10uA,#1         | COM-n |      |      | 0.2  |      |

| Output "L" Voltage  | Vol2e  | Iol=10uA,#2         |       |      |      | 0.2  |      |

|                     | Vol3e  | Iol=10uA,#3         |       |      |      | 0.2  |      |

|                     |        | 1/2 Bias Display    | Mode  |      |      |      |      |

|                     | Voh12f | Ioh=-1uA,#1,#2      |       | 2.2  |      |      |      |

| Output "H" Voltage  | Voh3f  | Ioh=-1uA,#3         |       | 3.8  |      |      | V    |

|                     | Vol12f | Iol=1uA,#1,#2       | SEG-n |      |      | 0.2  |      |

| Output "L" Voltage  | Vol3f  | Iol=1uA,#3          |       |      |      | 0.2  |      |

| Output "H" Voltage  | Voh12g | Ioh=-10uA,#1,#2     |       | 2.2  |      |      |      |

|                     | Voh3g  | Ioh=-10uA,#3        |       | 3.8  |      |      |      |

|                     | Vom12g | Iol/h=+/-10uA,#1,#2 |       | 1.0  |      | 1.4  |      |

| Output "M" Voltage  | Vom3g  | Iol/h=+/-10uA,#3    | COM-n | 1.8  |      | 2.2  |      |

|                     | Vol12g | Iol=10uA,#1,#2      |       |      |      | 0.2  |      |

| Output "L" Voltage  | Vol3g  | Iol=10uA,#3         |       |      |      | 0.2  |      |

|                     | 1      | 1/3 Bias display    | Mode  |      | 1    |      |      |

|                     | Voh12i | Ioh=-1uA,#1,#2      |       | 3.4  |      |      |      |

| Output "H" Voltage  | Voh3i  | Ioh=-1uA,#3         |       | 5.8  |      |      |      |

| O-4                 | Vom12i | Iol/h=+/-10uA,#1,#2 |       | 1.0  |      | 1.4  |      |

| Output "M1" Voltage | Vom13i | Iol/h=+/-10uA,#3    |       | 1.8  |      | 2.2  |      |

|                     | Vom22i | Iol/h=+/-10uA,#1,#2 | SEG-n | 2.2  |      | 2.6  |      |

| Output "M2" Voltage | Vom23i | Iol/h=+/-10uA,#3    |       | 3.8  |      | 4.2  | 1    |

|                     | Vol12i | Iol=1uA,#1,#2       |       |      |      | 0.2  |      |

| Output "L" Voltage  | Vol3i  | Iol=1uA,#3          |       |      |      | 0.2  | **   |

|                     | Voh12j | Ioh=-10uA,#1,#2     |       | 3.4  |      |      | V    |

| Output "H" Voltage  | Voh3j  | Ioh=-10uA,#3        |       | 5.8  |      |      |      |

|                     | Vom12j | Iol/h=+/-10uA,#1,#2 | -     | 1.0  |      | 1.4  | -    |

| Output "M1" Voltage | Vom13j | Iol/h=+/-10uA,#3    | 0014  | 1.8  |      | 2.2  |      |

|                     | Vom22j | Iol/h=+/-10uA,#1,#2 | COM-n | 2.2  |      | 2.6  |      |

| Output "M2" Voltage | Vom23j | Iol/h=+/-10uA,#3    |       | 3.8  | 1    | 4.2  |      |

|                     | Vol12j | Iol=10uA,#1,#2      |       |      |      | 0.2  |      |

| Output "L" Voltage  | Vol3j  | Iol=10uA,#3         |       |      |      | 0.2  |      |

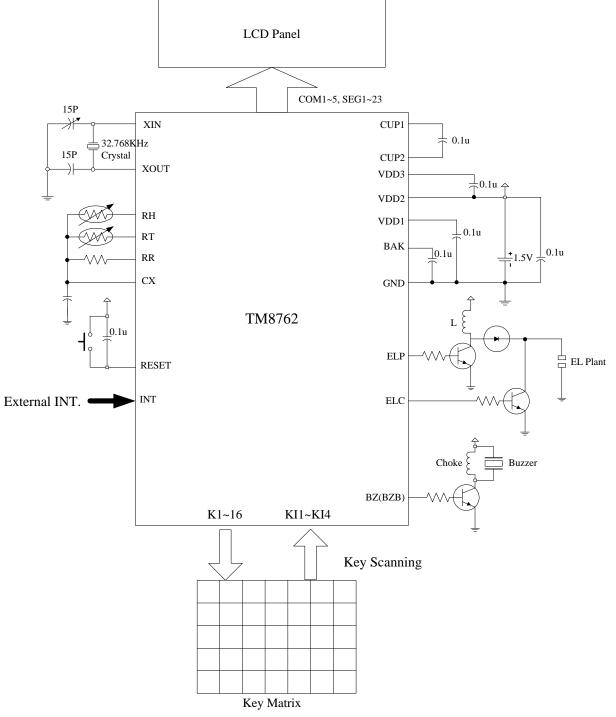

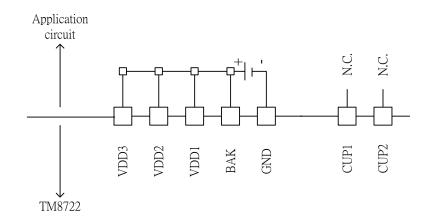

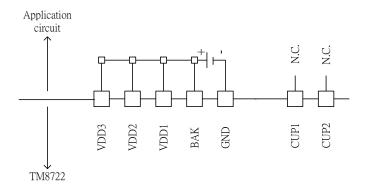

# **1.8 TYPICAL APPLICATION CIRCUIT**

This application circuit is only an example, and can not be guaranteed to work.

# 2. TM8762 Internal System Architecture

# 2.1 Power Supply

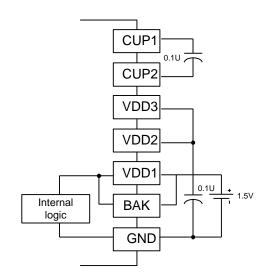

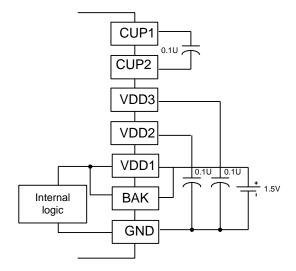

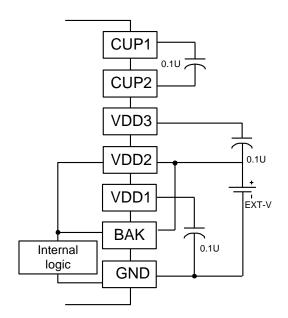

TM8762 can operate using 3 types of supply voltage: Ag, Li, and EXTV, which can be selected in mask option. The power supply circuitry selected will also provide the necessary voltage level to drive the LCD panel with different biases. The connection diagrams for 1/2 bias,1/3 bias and no bias applications are shown below.

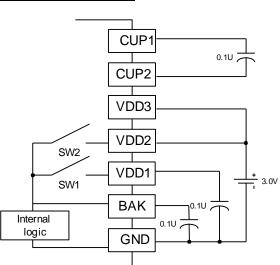

### 2.1.1 Ag BATTERY POWER SUPPLY

Operating voltage range : 1.2V ~ 1.8V.

The connection diagrams for different LCD bias applications are shown below:

# 2.1.1.1 NO LCD BIAS NEEDED using a Ag BATTERY POWER SUPPLY

MASK OPTION table:

| Mask Option name | Selected item    |

|------------------|------------------|

| POWER SOURCE     | (3) 1.5V BATTERY |

| LCD BIAS         | (3) NO BIAS      |

Note 1: The input/output ports operate between GND and VDD1.

**Note 2:** The backup flag (BCF) is set to 1 in the initial reset cycle. When as the backup flag is set to 1, the driving capability of the oscillator circuit increases, it improves the oscillation conditions but the operating current also increases. Therefore, unless it is required, otherwise, the backup flag must be reset to 0 after the initial reset cycle. For the the backup flag, please refer to 3-5.

# 2.1.1.2 1/2 BIAS & STATIC using a AG BATTERY POWER SUPPLY

MASK OPTION table:

| Mask Option name | Selected item    |

|------------------|------------------|

| POWER SOURCE     | (3) 1.5V BATTERY |

| LCD BIAS         | (2) 1/2 BIAS     |

Note 1: The input/output ports operate between GND and VDD1.

**Note 2:** The backup flag (BCF) is set to 1 in the initial reset cycle. When the backup flag is set to 1, the driving power of the oscillator circuit increases, it improves the oscillation conditions but the operating current also increases. Therefore, unless it is required, otherwise, the backup flag must be reset to 0 after the initial reset cycle. For the backup flag, please refer to 3-5.

# 2.1.1.3 1/3 BIAS using a AG BATTERY POWER SUPPLY

MASK OPTION table:

| Mask Option name | Selected item    |

|------------------|------------------|

| POWER SOURCE     | (3) 1.5V BATTERY |

| LCD BIAS         | (1) 1/3 BIAS     |

Note 1: The input/output ports operate between GND and VDD1.

Note 2: The backup flag (BCF) is set to 1 in the initial reset cycle. When the backup flag is set to 1, the driving power of the oscillator circuit increases, it improves the oscillation conditions but the operating current also increases. Therefore, unless it is required, otherwise, the backup flag must be reset to 0 after the initial reset cycle. For the backup flag, please refer to 3-5.

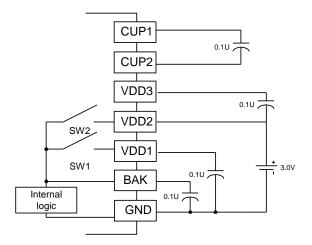

### 2.1.2 LI BATTERY POWER SUPPLY

Operating voltage range : 2.4V ~ 3.6V.

The connection diagrams for different LCD bias applications are shown below :

### 2.1.2.1 NO BIAS using a LI BATTERY POWER SUPPLY

MASK OPTION table :

| Mask Option name | Selected item            |

|------------------|--------------------------|

| POWER SOURCE     | (2) 3V BATTERY OR HIGHER |

| LCD BIAS         | (3) NO BIAS              |

Note 1: The input/output ports operate between GND and VDD2.

# 2.1.2.2 1/2 BIAS using a LI BATTERY POWER SUPPLY

The backup flag (BCF) must be reset after the operation of the halver circuit is fully stabilized and a voltage of approximately 1/2 \* VDD2 appears on the VDD1 pin.

| Backup flag(BCF) | SW1 | SW2 |

|------------------|-----|-----|

| BCF=0            | ON  | OFF |

| BCF=1            | OFF | ON  |

MASK OPTION table:

| Mask Option name | Selected item     |

|------------------|-------------------|

| POWER SOURCE     | (2) 3V BATTERY OR |

| FOWER SOURCE     | HIGHER            |

| LCD BIAS         | (2) 1/2 BIAS      |

Note 1: The input/output ports operate between GND and VDD2.

- Note 2: The backup flag (BCF) is set to 1 in the initial reset cycle. When the backup flag is set to 1, the internal logic signal operated on VDD2 and the driving power of the oscillator circuit increases and the operating current also increases. Therefore, unless it is required, otherwise, the backup flag must be reset to 0 after the initial reset cycle. For the backup flag, please refer to 3-5.

- Note 3: The VDD1 level ( $\approx 1/2 * VDD2$ ) in the off-state of SW1 is used as an intermediate voltage level for the LCD driver.

### 2.1.2.3 1/3 BIAS using a LI BATTERY POWER SUPPLY

The backup flag (BCF) must be reset after the operation of the halver circuit is fully stabilized and a voltage of approximately 1/2 \* VDD2 appears on the VDD1 pin.

| Backup flag(BCF) | SW1 | SW2 |

|------------------|-----|-----|

| BCF=0            | ON  | OFF |

| BCF=1            | OFF | ON  |

### MASK OPTION table:

| Mask Option name | Selected item            |

|------------------|--------------------------|

| POWER SOURCE     | (2) 3V BATTERY OR HIGHER |

| LCD BIAS         | (1) 1/3 BIAS             |

Note 1: The input/output ports operate between GND and VDD2.

- **Note 2:** The backup flag (BCF) is set to 1 in the initial reset cycle. When the backup flag is set to 1, the internal logic signal operated on VDD2 and the driving power of the oscillator circuit increases and the operating current also increases. Therefore, unless it is required, otherwise, the backup flag must be reset to 0 after the initial reset cycle. For the backup flag, please refer to 3-5.

- Note 3: The VDD1 level (≈□ 1/2 \* VDD) in the off-state of SW1 is used as an intermediate voltage level for LCD driver.

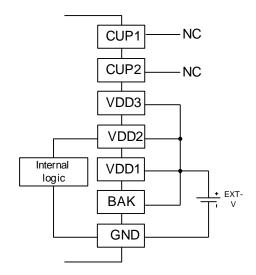

# 2.1.3 EXTV POWER SUPPLY

Operating voltage range : 3.6V ~ 5.4V.

The connection diagrams for different LCD bias applications are shown below :

# 2.1.3.1 NO BIAS using an EXT-V BATTERY POWER SUPPLY

#### MASK OPTION table:

| Mask Option name | Selected item |

|------------------|---------------|

| POWER SOURCE     | (1) EXT-V     |

| LCD BIAS         | (3) NO BIAS   |

Note 1: The input/output ports operate between GND and VDD2.

Note 2: the backup flag (BCF) is reset to 0 in the initial reset cycle.

Note 3: When the backup flag is set to 1, the operating current increases.

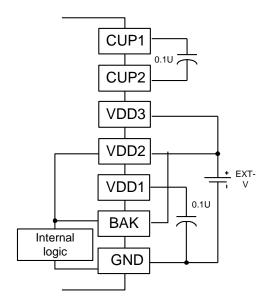

### 2.1.3.2 1/2 BIAS using an EXT-V POWER SUPPLY

#### MASK OPTION table:

| Mask Option name | Selected item |

|------------------|---------------|

| POWER SOURCE     | (1) EXT-V     |

| LCD BIAS         | (2) 1/2 BIAS  |

#### Note :

- 1. The input/output ports operate between GND and VDD2.

- 2. the backup flag (BCF) is reset to 0 in the initial reset cycle.

- **3.** When the backup flag is set to 1, the operating current increases. Therefore, unless it is required, otherwise, the backup flag must be reset to 0 in normal mode.

### 2.1.3.3 1/3 BIAS using an EXT-V POWER SUPPLY

MASK OPTION table:

| Mask Option name | Selected item |

|------------------|---------------|

| POWER SOURCE     | (1) EXT-V     |

| LCD BIAS         | (1) 1/3 BIAS  |

Note 1: The input/output ports operate between GND and VDD2.

Note 2: the backup flag (BCF) is reset to 0 in the initial reset cycle.

**Note 3:** When the backup flag is set to 1, the operating current increases. Therefore, unless it is required, otherwise, the backup flag must be reset to 0 in normal mode.

# 2.2 SYSTEM CLOCK

The clock oscillation circuitry consists of a XT clock (slow clock) oscillator and a CF clock (fast clock) oscillator. The output from this circuitry forms the clock source for the system clock generator (provides the necessary clock signals for the execution of instructions), the pre-divider (generates several clock signals with different frequencies to be used by the LCD driver), and for the frequency generator etc.

The following table shows the clock sources of system clock generator and the pre-divider under different conditions.

|                                  | PH0(per-divider) | BCLK(system clock) |

|----------------------------------|------------------|--------------------|

| Slow clock only option           | XT clock         | XT clock           |

| fast clock only option           | CF clock         | CF clock           |

| Initial state(dual clock option) | XT clock         | XT clock           |

| Halt mode(dual clock option)     | XT clock         | XT clock           |

| Slow mode(dual clock option)     | XT clock         | XT clock           |

| Fast mode(dual clock option)     | XT clock         | CF clock           |

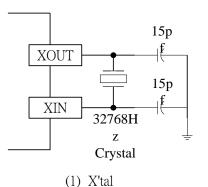

### 2.2.1 CONNECTION DIAGRAM OF THE SLOW CLOCK OSCILLATOR (XT CLOCK)

This clock oscillator provides the lower speed clock signals to the system clock generator, the pre-divider, the timer, the chattering prevention of the IO port and the LCD circuitry. This oscillator is disabled when the "fast clock only "option is selected in mask option, otherwise it is active all the time after the initial reset cycle. In stop mode, this oscillator will be stopped.

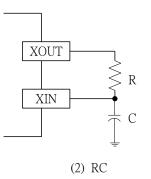

There are 2 types of oscillators that can be used as the slow clock oscillator, which can be selected in mask option:

### 2.2.1.1 External 32.768KHz Crystal oscillator (XT CLOCK)

MASK OPTION table:

| Selected item |

|---------------|

| (1) X'tal     |

|               |

When the backup flag (BCF) is set to 1, the oscillator operates in a state with a higher driving capability and the start-up time of the oscillator can be reduced as a result. However it increases the power consumption. Therefore, the backup flag should be reset unless required otherwise.

The following table shows the power consumption of Crystal oscillator under different conditions:

|               | Ag power option | Li power option | EXT-V option |

|---------------|-----------------|-----------------|--------------|

| BCF=1         | Increase        | Increase        | Increase     |

| BCF=0         | Normal          | Normal          | Increase     |

| Initial reset | Increase        | Increase        | Increase     |

| After reset   | Increase        | Increase        | Increase     |

# 2.2.1.2 External RC oscillator (XT CLOCK)

MASK OPTION table:

| Mask Option name                      | Selected item |

|---------------------------------------|---------------|

| SLOW CLOCK TYPE FOR SLOW ONLY OR DUAL | (2) RC        |

# 2.2.2 CONNECTION DIAGRAM OF THE FAST CLOCK OSCILLATOR (CF CLOCK)

The CF clock consists of 3 types of oscillators (selectable in mask option) which provides a faster clock sources to the system. In single clock operation (fast only), this oscillator provides the clock signals to the system clock generator, the pre-divider, the timer, the I/O port chattering prevention clock and the LCD circuitry. In dual clock operation, CF clock provides the clock signals to the system clock generator only.

When the dual clock option is selected in mask option, this oscillator is inactive most of the time except when the FAST instruction is executed. After the FAST instruction is executed, the clock source (BCLK) of the system clock generator will be switched to CF clock but the clock source for other functions will still come in from the XT clock. The Halt mode, the stop mode and the execution of the SLOW instruction will stop this oscillator and the system clock (BCLK) will be switched to the XT clock.

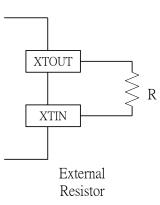

There are 3 types of oscillators that can be used as the fast clock oscillator, which can be selected in mask option:

# 2.2.2.1 RC OSCILLATOR WITH EXTERNAL RESISTOR (CF CLOCK)

This type of oscillator can only be used in the "FAST only" option, however, this oscillator can not be used as the fast clock source in dual clock mode. When this oscillator is selected in mask option, the RC oscillator with internal RC will be disabled.

### MASK OPTION table:

| Mask Option name | Selected item                         |

|------------------|---------------------------------------|

| CLOCK SOURCE     | (2) FAST ONLY & USE EXTERNAL RESISTOR |

#### MASK OPTION table:

| Mask Option name                          | Selected item          |

|-------------------------------------------|------------------------|

| FAST CLOCK OSC TYPE FOR FAST ONLY OR DUAL | (1) or (2), don't care |

### 2.2.2.2 RC OSCILLATOR WITH INTERNAL RESISTOR (CF CLOCK)

Two frequencies can be selected in this type of oscillator: 250KHz and 500KHz. When the oscillator is used, CFOUT and CFIN pins should be left open.

This type of oscillator can be used both in the "FAST only" and the "DUAL clock" options.

MASK OPTION table:

| Mask Option name | Selected item                                     |

|------------------|---------------------------------------------------|

| CLOCK SOURCE     | (1) FAST ONLY & USE EXTERNAL RESISTOR or (4) DUAL |

For 250KHz output frequency :

| Mask Option name                          | Selected item                    |

|-------------------------------------------|----------------------------------|

| FAST CLOCK OSC TYPE FOR FAST ONLY OR DUAL | (1) INTERNAL RESISTOR FOR 250KHz |

For 500KHz output frequency:

| Mask Option name                          | Selected item                    |

|-------------------------------------------|----------------------------------|

| FAST CLOCK OSC TYPE FOR FAST ONLY OR DUAL | (2) INTERNAL RESISTOR FOR 500KHz |

### FREQUENCY RANGE OF INTERNAL RC OSCILLATOR

| Option Mode | BAK  | Min.    | Тур.    | Max.    |

|-------------|------|---------|---------|---------|

| 250 KHz     | 1.5V | 200 KHz | 300 KHz | 400 KHz |

| 230 KHZ     | 3.0V | 200 KHz | 250 KHz | 300 KHz |

| 500 KU      | 1.5V | 450 KHz | 600 KHz | 750 KHz |

| 500 KHz     | 3.0V | 400 KHz | 500 KHz | 600 KHz |

# 2.2.3 COMBINATION OF THE CLOCK SOURCES (CLCOK SWITCH CIRCUIT)

The clock switch circuit allows the selection of different clock inputs from XTOSC and CFOSC. There are three combinations of the clock sources that can be selected in mask option:

### 2.2.3.1 DUAL CLOCK

MASK OPTION table:

| Mask Option name | Selected item |

|------------------|---------------|

| CLOCK SOURCE     | (4) DUAL      |

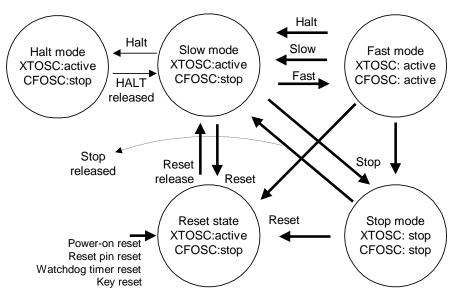

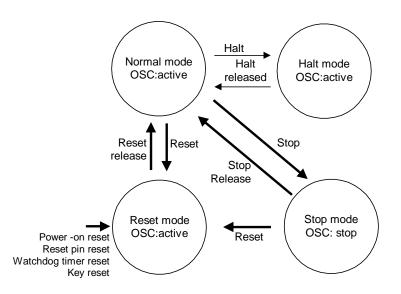

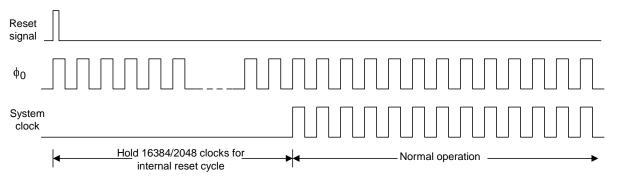

The operation of the dual clock mode is shown in the following figure.

When this mode is selected in mask option, the clock source (BCLK) of the system clock generator will switch between XT clock and CF clock according to the user's program. When the HALT and STOP instructions are executed, the clock source (BCLK) will switch to the XT clock automatically.

The XT clock provides the clock signals to the pre-divider, the timer, the I/O port chattering prevention and the LCD circuitry in this mode.

The state diagram of the dual clock mode is shown in the above figure.

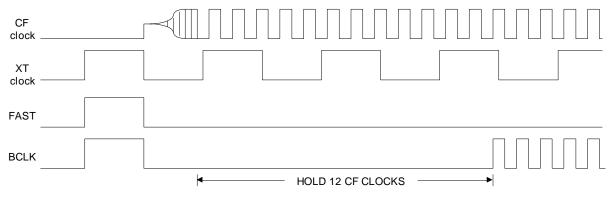

After the execution of the FAST instruction, the system clock generator will hold for 12 CF clock cycles after the CF clock oscillator starts up and then BCLK will switch to the CF clock. It prevents the delivery of incorrect clock signals to the system clock in the start-up duration of the fast clock oscillator.

This figure shows the System Clock Switches from Slow to Fast

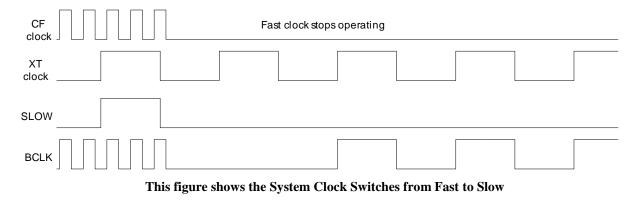

After executing SLOW instruction, the system clock generator will hold for 2 XT clock cycles and then BCLK will switch to the XT clock.

# 2.2.3.2 SINGLE CLOCK

#### MASK OPTION table:

For Fast clock oscillator only

| Mask Option name | Selected item                                                                                                    |

|------------------|------------------------------------------------------------------------------------------------------------------|

| CLOCK SOURCE     | <ul><li>(1) FAST ONLY &amp; USE INTERNAL RESISTOR</li><li>or (2) FAST ONLY &amp; USE EXTERNAL RESISTOR</li></ul> |

For slow clock oscillator only

| Mask Option name | Selected item |

|------------------|---------------|

| CLOCK SOURCE     | (3) SLOW ONLY |

The operation of the single clock option is shown in the following figure.

Either XT or CF clock can be selected in mask option in this mode. The FAST and SLOW instructions will be treated as the NOP instruction in this mode.

The backup flag (BCF) will be set to 1 automatically before the program enters the stop mode. It can ensure that the Crystal oscillator starts up in a favorable condition.

This figure shows the State Diagram of Single Clock Option

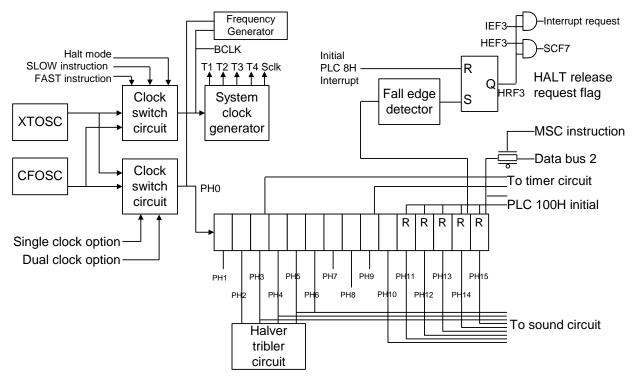

### 2.2.4 PREDIVIDER

The pre-divider is a 15-stage counter that receives the clock signals from the output of the clock switch circuitry (PH0). When PH0 changes from "H" level to "L" level, the content of this counter changes accordingly. The PH11 to PH15 of the pre-divider are reset to "0" when the PLC 100H instruction is executed or in the initial reset cycle.

The pre-divider delivers the signals to the halver/tripler circuit, the LCD driver, the sound generator and the I/O port chattering prevention function.

This figure shows the pre-divider and its peripherals

The falling edge of PH14 will set the halt mode release request flag (HRF3) to 1, and if the pre-divider interrupt enable mode (IEF3) was also set in advance, the interrupt comes from predivider will be accepted; and if the halt release enable mode (HEF3) was also set in advance, then the halt release request signal will be delivered and the start condition flag 7 (SCF7) in status register 3 (STS3) will be set.

The clock source of the pre-divider is PH0, there are 4 kinds of frequencies of PH0 that can be selected in mask option:

MASK OPTION table:

| Mask Option name           | Selected item      |

|----------------------------|--------------------|

| PH0 <-> BCLK FOR FAST ONLY | (1) $PH0 = BCLK$   |

| PH0 <-> BCLK FOR FAST ONLY | (2) $PH0 = BCLK/4$ |

| PH0 <-> BCLK FOR FAST ONLY | (3) PH0 = BCLK/8   |

| PH0 <-> BCLK FOR FAST ONLY | (4) PH0 = BCLK/16  |

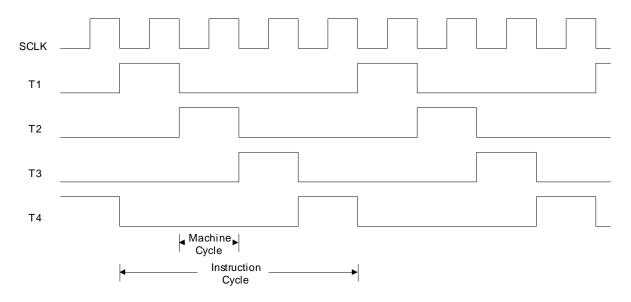

### 2.2.5 SYSTEM CLOCK GENERATOR

The system clock generator provides the necessary clock signals to control the execution of instructions.

The FAST and SLOW instructions can also be used to switch the clock input of the system clock generator.

The basic system clock is shown below:

# 2.3 PROGRAM COUNTER (PC)

The program counter is a 11-bit counter, which addresses the program memory (ROM) up to 2048 addresses.

- The program counter (PC) is normally incremented by one (+1) for every instruction execution.

PC ← PC + 1

- When executing JMP instruction, subroutine call instruction (CALL), interrupt service routine or when reset occurs, the program counter (PC) will be loaded with the corresponding address in table 2-1.

- $PC \leftarrow corresponding address shown in$

Table 2-1

- When executing a jump instruction except JMP and CALL, the program counter (PC) will be loaded with the specified address in the operand of the instruction.

- PC  $\leftarrow$  current page (PC11) + specified address in the operand

- Return instruction (RTS)

- PC  $\leftarrow$  content of stack specified by the stack pointer Stack pointer  $\leftarrow$  stack pointer -1

| Table  | 2- | 1 |

|--------|----|---|

| I uore | _  |   |

|                                         | PC10 | PC9 | PC8 | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 |

|-----------------------------------------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Initial reset                           | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Interrupt 2<br>(INT pin)                | 0    | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 0   |

| Interrupt 0<br>(input port C)           | 0    | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 1   | 0   | 0   |

| Interrupt 1<br>(timer 1 interrupt)      | 0    | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 0   | 0   | 0   |

| Interrupt 3<br>(pre-divider interrupt)  | 0    | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 1   | 0   | 0   |

| Interrupt 4<br>(timer 2 interrupt)      | 0    | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 0   | 0   |

| Interrupt 5<br>(Key Scanning interrupt) | 0    | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 1   | 0   | 0   |

| Interrupt 6<br>(RFC counter interrupt)  | 0    | 0   | 0   | 0   | 0   | 1   | 0   | 1   | 0   | 0   | 0   |

| Jump instruction                        | P10  | P9  | P8  | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

| Subroutine call                         | P10  | P9  | P8  | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

P10 to P0 : the **11** Low-order bits of instruction operand.

When executing a subroutine call or an interrupt service routine, the contents of the program counter (PC) will be automatically saved to the stack register (STACK).

# 2.4 PROGRAM/TABLE MEMORY

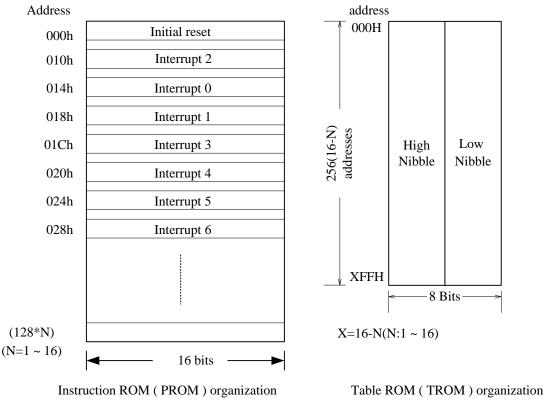

The built-in mask ROM is organized into 2048 x 16 bits.

Both instruction ROM (PROM) and table ROM (TROM) share this memory space together. The partition formula for PROM and TROM is shown below:

Instruction ROM memory space = (128 \* N) words,

Table ROM memory space = 256(16 - N) bytes (N=1~16).

**Note :** The data width of the table ROM is 8-bit

The partition of memory space is defined in mask option, the table is shown below:

# MASK OPTION table :

|                               |               | Instruction ROM | Table ROM memory |

|-------------------------------|---------------|-----------------|------------------|

| Mask Option name              | Selected item | memory space    | space            |

|                               |               | (Words)         | (Bytes)          |

|                               | 1 (N=1)       | 128             | 3840             |

|                               | 2 (N=2)       | 256             | 3584             |

|                               | 3 (N=3)       | 384             | 3328             |

|                               | 4 (N=4)       | 512             | 3072             |

|                               | 5 (N=5)       | 640             | 2816             |

|                               | 6 (N=6)       | 768             | 2560             |

|                               | 7 (N=7)       | 896             | 2304             |

| INSTRUCTION ROM <-> TABLE ROM | 8 (N=8)       | 1024            | 2048             |

| INSTRUCTION ROW <-> TABLE ROW | 9 (N=9)       | 1152            | 1792             |

|                               | A (N=10)      | 1280            | 1536             |

|                               | B (N=11)      | 1408            | 1280             |

|                               | C (N=12)      | 1536            | 1024             |

|                               | D (N=13)      | 1664            | 768              |

|                               | E (N=14)      | 1792            | 512              |

|                               | F (N=15)      | 1920            | 256              |

|                               | G (N=16)      | 2048            | 0                |

# 2.4.1 INSTRUCTION ROM (PROM)

There are some special locations that serve as the interrupt service routines, such as reset address (000H), interrupt 0 address (014H), interrupt 1 address (018H), interrupt 2 address (010H), interrupt 3 address (01CH), interrupt 4 address (020H), interrupt 5 address (024H), and interrupt 6 address (028H) in the program memory.

This figure shows the Organization of ROM

# 2.4.2 TABLE ROM (TROM)

The table ROM is organized into  $256(16-N) \ge 8$  bits that shares the memory space with instruction ROM, as shown in the figure above. This memory space stores the constant data or look up tables for the usage of the main program. All table ROM addresses can be specified by the index address register (@HL). The data width can be 8 bits ( $256(16-N) \ge 8$  bits) or 4 bits ( $512(16-N) \ge 4$  bits) depending on the usage. Please refer to the explanation in the instruction chapter for details.

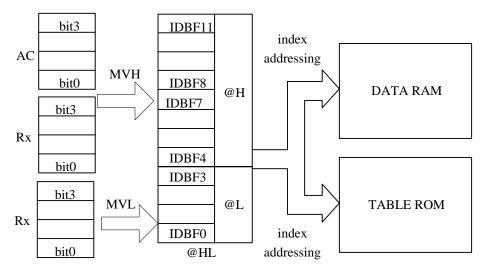

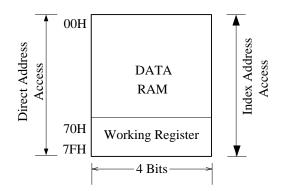

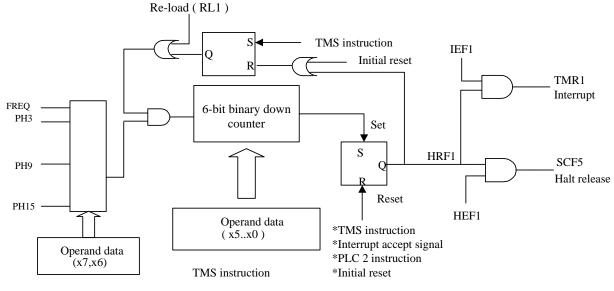

# 2.5 INDEX ADDRESS REGISTER (@HL)